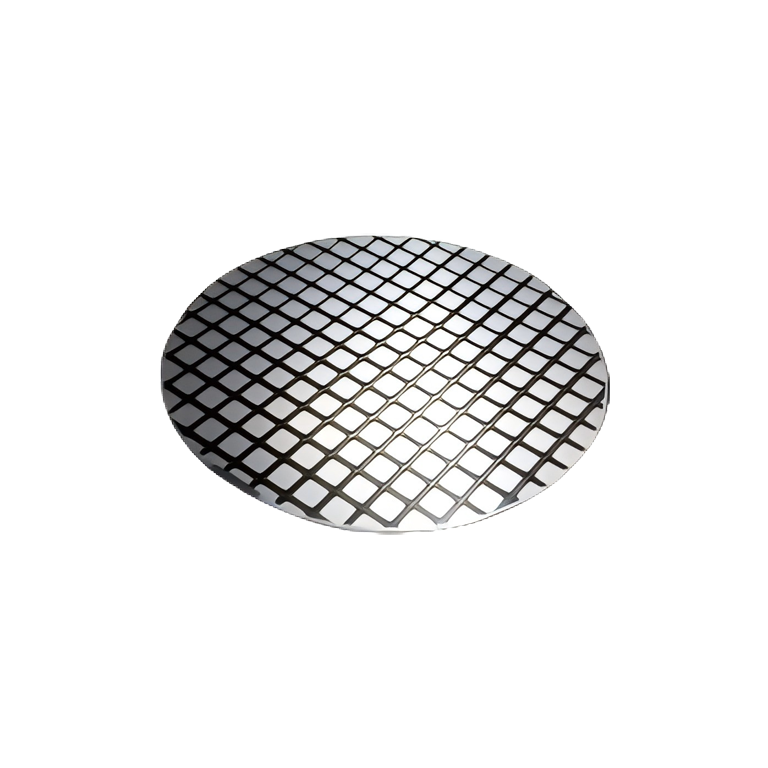

The semiconductor industry has witnessed remarkable transformations in power electronics, with IGBT wafer technology standing at the forefront of these advancements. The evolution of trench field stop IGBT wafer designs represents a paradigm shift from conventional planar structures to sophisticated vertical architectures that deliver superior performance characteristics. This technological progression has fundamentally altered how power semiconductor devices manage electrical conduction, switching speeds, and thermal dissipation in high-voltage applications across industrial sectors.

The journey from first-generation planar IGBT wafer structures to modern trench field stop configurations reflects decades of material science breakthroughs, manufacturing process refinements, and design optimization efforts. Each evolutionary step has addressed specific performance limitations while introducing new capabilities that extend the operational boundaries of power electronic systems. Understanding this technological evolution provides crucial insights into current IGBT wafer capabilities and future development trajectories that will shape power electronics applications in renewable energy, electric vehicles, and industrial automation.

Historical Development Phases of IGBT Wafer Architecture

First Generation Planar IGBT Wafer Foundations

The initial IGBT wafer designs emerged in the 1980s as hybrid devices combining the voltage handling capabilities of MOSFETs with the current carrying capacity of bipolar junction transistors. Early planar IGBT wafer structures featured horizontal gate channels fabricated on the silicon surface, establishing the fundamental operating principles that would guide subsequent innovations. These pioneering designs demonstrated the viability of voltage-controlled power switching while revealing limitations in switching speed and conduction efficiency that would drive future evolutionary steps.

Manufacturing processes for first-generation IGBT wafer production relied heavily on established silicon processing techniques adapted from discrete semiconductor fabrication. The planar architecture simplified manufacturing complexity while providing adequate performance for initial power electronic applications in motor drives and power supplies. However, the horizontal channel configuration inherently limited current density and introduced parasitic resistances that constrained overall device efficiency.

Performance characteristics of early IGBT wafer devices exhibited trade-offs between blocking voltage capability and switching speed that reflected the fundamental physics of planar channel structures. The collector-emitter saturation voltage remained relatively high compared to modern standards, while switching losses represented significant portions of total power dissipation in high-frequency applications. These limitations established the technical motivation for advancing toward more sophisticated wafer architectures.

Transition to Vertical Channel Configurations

The migration from planar to vertical channel IGBT wafer designs marked a critical evolutionary milestone that addressed fundamental limitations of horizontal gate structures. Vertical channels enabled more efficient utilization of silicon wafer area while reducing the conductive path length between source and drain regions. This architectural shift required significant advances in deep etching processes and precise doping profile control to maintain device reliability and performance consistency.

Manufacturing complexity increased substantially during the transition to vertical IGBT wafer architectures, necessitating new equipment capabilities and process control methodologies. Deep reactive ion etching techniques became essential for creating uniform vertical channels with controlled sidewall profiles and minimal surface damage. The integration of these advanced processing steps demanded extensive process development efforts and quality control procedures to ensure consistent wafer-level performance.

Performance improvements achieved through vertical channel IGBT wafer designs included reduced on-state voltage drop, improved current handling capacity, and enhanced switching speed characteristics. The shortened current path and increased channel density per unit area directly translated to lower conduction losses and improved thermal management capabilities. These advantages established vertical architectures as the foundation for subsequent IGBT wafer evolution toward field stop configurations.

Trench Technology Integration and Optimization

Deep Trench Formation Processes

The implementation of trench structures in IGBT wafer manufacturing represents a sophisticated integration of advanced semiconductor processing techniques with precision dimensional control. Deep trench formation requires specialized etching processes capable of creating vertical sidewalls with aspect ratios exceeding 10:1 while maintaining uniform width dimensions across the entire wafer surface. These processes utilize carefully controlled plasma chemistry and magnetic field configurations to achieve the necessary etch selectivity and profile control.

Process optimization for trench IGBT wafer production involves complex interactions between etch rate uniformity, sidewall smoothness, and dimensional accuracy across varying feature densities. Advanced process monitoring systems continuously track etch depth progression, sidewall angle variations, and surface contamination levels to ensure consistent results. The integration of real-time feedback control systems enables automatic adjustment of process parameters to compensate for equipment drift and wafer-to-wafer variations.

Quality control measures for trench formation include comprehensive metrology protocols that verify dimensional accuracy, sidewall integrity, and surface cleanliness at multiple process stages. Scanning electron microscopy analysis provides detailed characterization of trench profiles and sidewall morphology, while atomic force microscopy enables quantitative assessment of surface roughness parameters. These analytical techniques ensure that each IGBT wafer meets stringent specifications for subsequent processing steps.

Gate Oxide and Polysilicon Deposition Advances

The formation of high-quality gate oxide layers within trench structures presents unique technical challenges that require specialized deposition and annealing processes. Conformal oxide growth on vertical sidewalls demands precise control of oxidation kinetics and stress management to prevent defect formation that could compromise device reliability. Advanced thermal oxidation processes utilize carefully controlled ambient compositions and temperature profiles to achieve uniform oxide thickness distribution throughout complex three-dimensional geometries.

Polysilicon gate electrode formation within trenches requires sophisticated chemical vapor deposition processes that ensure complete filling without void formation or stress concentration. The deposition process parameters must be optimized to achieve adequate step coverage while maintaining acceptable film uniformity and electrical properties. Subsequent planarization processes remove excess polysilicon material while preserving precise gate electrode geometry and surface planarity required for subsequent metallization steps.

Interface quality between gate oxide and polysilicon electrodes directly impacts the electrical characteristics and long-term reliability of trench IGBT wafer devices. Advanced characterization techniques including capacitance-voltage measurements and charge pumping analysis provide detailed assessment of interface state density and charge trapping behavior. These measurements guide process optimization efforts to minimize interface defects that could degrade switching performance or reduce operational lifetime.

Field Stop Layer Implementation and Engineering

Ion Implantation Profile Design

The field stop layer represents a critical innovation in modern IGBT wafer technology that enables precise control of electric field distribution within the device structure. Implementation of field stop layers requires sophisticated ion implantation processes that create controlled doping profiles at specific depths within the silicon substrate. The implantation energy and dose parameters must be carefully optimized to achieve the desired field shaping effects while maintaining compatibility with thermal processing requirements.

Design optimization for field stop layer profiles involves complex modeling of electric field distribution and carrier dynamics under various operating conditions. Advanced device simulation tools enable evaluation of different doping profile shapes and concentrations to identify configurations that maximize blocking voltage capability while minimizing impact on switching performance. The integration of field stop layers requires careful consideration of interaction effects with other device regions including the drift layer and collector structure.

Manufacturing control for field stop layer implementation demands precise monitoring of implantation parameters and subsequent thermal activation processes. Ion beam current uniformity, energy stability, and dose accuracy directly impact the resulting doping profile and device performance characteristics. Advanced process control systems continuously monitor implantation conditions and provide real-time feedback to maintain consistent results across multiple IGBT wafer processing batches.

Thermal Activation and Profile Refinement

The thermal activation of implanted field stop layers requires carefully controlled annealing processes that activate dopant atoms while minimizing unwanted diffusion and defect generation. High-temperature annealing cycles must be optimized to achieve complete electrical activation of implanted species while preserving the precise doping profile shape required for optimal device performance. Advanced rapid thermal processing techniques enable precise temperature and time control to achieve desired activation levels.

Process integration challenges for field stop layer thermal treatment include managing thermal budget limitations and avoiding degradation of previously formed device structures. The annealing conditions must be compatible with gate oxide integrity requirements while providing sufficient thermal energy for dopant activation. Multiple annealing step sequences may be employed to achieve optimal activation while maintaining overall process compatibility.

Characterization of field stop layer effectiveness involves comprehensive electrical testing and physical analysis to verify proper profile formation and electrical activity. Secondary ion mass spectrometry provides detailed dopant concentration profiles that can be compared with design targets and simulation predictions. Electrical measurements including breakdown voltage testing and capacitance-voltage analysis confirm proper field stop layer functionality and performance enhancement.

Performance Enhancements and Modern Capabilities

Switching Speed Improvements

Modern trench field stop IGBT wafer technology delivers substantial improvements in switching speed performance compared to earlier generation devices. The combination of vertical channel architecture and optimized field stop layers reduces switching losses by minimizing charge storage effects and improving carrier extraction efficiency during turn-off transitions. These enhancements enable higher switching frequencies while maintaining acceptable power dissipation levels in demanding applications.

The switching performance characteristics of advanced IGBT wafer devices reflect sophisticated optimization of multiple design parameters including channel density, gate oxide thickness, and drift layer resistivity. Modern devices achieve turn-on times measured in hundreds of nanoseconds while maintaining controlled turn-off behavior that minimizes electromagnetic interference generation. The improved switching speed capabilities expand the application range for IGBT wafer technology into higher frequency power conversion systems.

Dynamic performance testing of modern IGBT wafer devices utilizes advanced characterization techniques that capture transient behavior under realistic operating conditions. Double-pulse testing methods enable precise measurement of switching losses and safe operating area boundaries while simulating actual circuit conditions. These comprehensive characterization efforts ensure that performance improvements translate to reliable operation in practical applications.

Thermal Management and Reliability Advances

The evolution of IGBT wafer technology has incorporated significant advances in thermal management capabilities that enhance device reliability and extend operational lifetime. Improved current distribution uniformity achieved through trench field stop designs reduces localized heating effects and thermal stress concentrations that could compromise device integrity. The enhanced current handling capability enables higher power density operation while maintaining acceptable junction temperatures.

Reliability improvements in modern IGBT wafer devices result from systematic optimization of material interfaces, process cleanliness, and structural design features that minimize failure mechanisms. Advanced wafer processing techniques reduce contamination levels and improve crystalline quality throughout the device structure. The implementation of redundant current paths and improved heat spreading characteristics enhance robustness against thermal cycling and electrical stress conditions.

Long-term reliability validation for advanced IGBT wafer technology involves comprehensive accelerated testing programs that evaluate device performance under elevated temperature, humidity, and electrical stress conditions. Statistical analysis of failure modes and degradation mechanisms provides valuable feedback for continued design optimization and process improvement efforts. These reliability enhancement measures ensure that performance improvements do not compromise the operational longevity expected in industrial applications.

FAQ

What are the main differences between planar and trench IGBT wafer structures?

Trench IGBT wafer structures feature vertical gate channels etched into the silicon surface, while planar designs utilize horizontal channels formed at the surface level. The vertical architecture of trench structures enables higher channel density per unit area, reduced conduction losses, and improved current handling capability. Trench designs also provide better control over electric field distribution and enable more compact device layouts compared to planar configurations.

How does the field stop layer improve IGBT wafer performance?

The field stop layer creates a controlled electric field profile that enhances voltage blocking capability while reducing switching losses. This engineered doping region prevents electric field crowding and enables thinner drift regions without compromising breakdown voltage ratings. The field stop implementation allows for reduced on-state voltage drop and faster switching transitions, significantly improving overall device efficiency in power electronic applications.

What manufacturing challenges are associated with trench field stop IGBT wafer production?

Manufacturing trench field stop IGBT wafer devices requires precise control of deep etching processes, conformal oxide growth, and ion implantation profiles. The complex three-dimensional geometry demands advanced process monitoring and quality control measures to ensure uniform performance across the wafer surface. Integration of multiple sophisticated processing steps increases manufacturing complexity and requires extensive process optimization to achieve acceptable yield levels.

How has IGBT wafer technology evolution impacted power electronics applications?

The evolution toward trench field stop IGBT wafer technology has enabled significant improvements in power conversion efficiency, switching frequency capability, and system reliability. These advances have expanded application possibilities in renewable energy systems, electric vehicle powertrains, and high-performance motor drives. The enhanced performance characteristics allow for more compact power electronic systems with reduced cooling requirements and improved overall system efficiency.

Table of Contents

- Historical Development Phases of IGBT Wafer Architecture

- Trench Technology Integration and Optimization

- Field Stop Layer Implementation and Engineering

- Performance Enhancements and Modern Capabilities

-

FAQ

- What are the main differences between planar and trench IGBT wafer structures?

- How does the field stop layer improve IGBT wafer performance?

- What manufacturing challenges are associated with trench field stop IGBT wafer production?

- How has IGBT wafer technology evolution impacted power electronics applications?