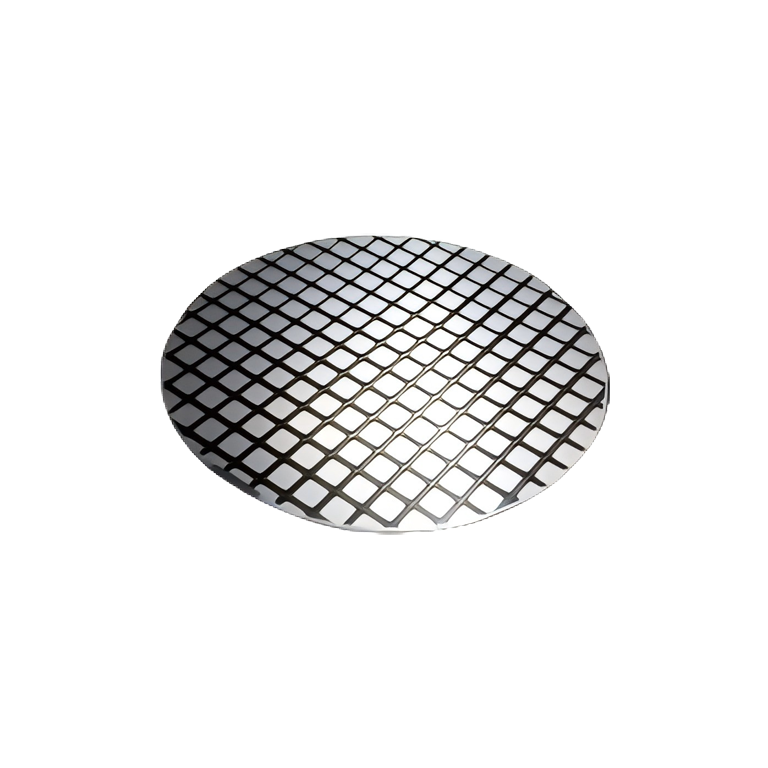

Le secteur des semi-conducteurs a connu des transformations remarquables dans le domaine de l’électronique de puissance, la technologie des wafers IGBT occupant une place centrale dans ces progrès. L’évolution des conceptions de wafers IGBT à tranchée et arrêt de champ marque un changement de paradigme par rapport aux structures planes conventionnelles, au profit d’architectures verticales sophistiquées offrant des caractéristiques de performance supérieures. Cette progression technologique a profondément modifié la façon dont les dispositifs semi-conducteurs de puissance gèrent la conduction électrique, les vitesses de commutation et la dissipation thermique dans les applications haute tension à travers les secteurs industriels.

Le parcours allant des structures de wafers IGBT planaires de première génération aux configurations modernes à tranchée avec arrêt de champ illustre des décennies de percées en sciences des matériaux, d’affinements des procédés de fabrication et d’efforts d’optimisation conceptionnelle. Chaque étape évolutive a permis de surmonter des limitations spécifiques de performance tout en introduisant de nouvelles fonctionnalités qui étendent les limites opérationnelles des systèmes électroniques de puissance. Comprendre cette évolution technologique fournit des éléments essentiels pour appréhender les capacités actuelles des wafers IGBT ainsi que les trajectoires de développement futures qui façonneront les applications de l’électronique de puissance dans les domaines de l’énergie renouvelable, des véhicules électriques et de l’automatisation industrielle.

Phases historiques du développement de l’architecture des wafers IGBT

Fondations des wafers IGBT planaires de première génération

Les premières conceptions de wafers IGBT sont apparues dans les années 1980 sous la forme de dispositifs hybrides combinant les capacités de tenue en tension des MOSFET et la capacité de transport de courant des transistors à jonction bipolaires. Les structures initiales de wafers IGBT planaires comportaient des canaux de grille horizontaux fabriqués à la surface du silicium, établissant ainsi les principes de fonctionnement fondamentaux qui guideraient les innovations ultérieures. Ces conceptions pionnières ont démontré la viabilité de la commutation de puissance commandée en tension, tout en révélant des limitations en matière de vitesse de commutation et d’efficacité de conduction, ce qui a stimulé les étapes évolutives suivantes.

Procédés de fabrication des premières générations Wafer IGBT la production reposait fortement sur des techniques établies de traitement du silicium, adaptées à la fabrication discrète de semi-conducteurs. L’architecture plane simplifiait la complexité de la fabrication tout en offrant des performances adéquates pour les premières applications électroniques de puissance dans les variateurs de vitesse et les alimentations électriques. Toutefois, la configuration horizontale du canal limitait intrinsèquement la densité de courant et introduisait des résistances parasites qui restreignaient l’efficacité globale du dispositif.

Les caractéristiques de performance des premiers dispositifs IGBT sur wafers présentaient des compromis entre la tension de blocage et la vitesse de commutation, reflétant la physique fondamentale des structures à canal plan. La tension de saturation collecteur-émetteur demeurait relativement élevée par rapport aux normes actuelles, tandis que les pertes de commutation représentaient une part significative de la dissipation totale de puissance dans les applications haute fréquence. Ces limitations ont constitué la motivation technique sous-jacente à l’évolution vers des architectures de wafers plus sophistiquées.

Passage aux configurations de canal verticales

La migration des conceptions de wafers IGBT à canal planaire vers des conceptions à canal vertical a marqué une étape décisive dans l’évolution de ces composants, permettant de surmonter les limitations fondamentales des structures de grille horizontales. Les canaux verticaux ont permis une utilisation plus efficace de la surface du wafer en silicium tout en réduisant la longueur du chemin conductif entre les régions source et drain. Ce changement architectural a nécessité des progrès significatifs dans les procédés de gravure profonde ainsi qu’un contrôle précis des profils de dopage afin de préserver la fiabilité du dispositif et la constance de ses performances.

La complexité de la fabrication a augmenté considérablement lors de la transition vers des architectures de wafers IGBT verticales, ce qui a nécessité de nouvelles capacités d’équipement et de nouvelles méthodologies de maîtrise des procédés. Les techniques de gravure ionique réactive profonde sont devenues essentielles pour créer des canaux verticaux uniformes, dotés de profils contrôlés des parois latérales et de dommages minimaux à la surface. L’intégration de ces étapes de traitement avancées a exigé des efforts importants de développement des procédés ainsi que des procédures rigoureuses de contrôle qualité afin d’assurer des performances cohérentes au niveau des wafers.

Les améliorations de performance obtenues grâce aux conceptions de wafers IGBT à canal vertical comprenaient une réduction de la chute de tension à l’état passant, une capacité accrue de gestion du courant et des caractéristiques améliorées de vitesse de commutation. Le raccourcissement du trajet du courant et l’augmentation de la densité de canaux par unité de surface se sont traduits directement par des pertes de conduction plus faibles et des capacités améliorées de gestion thermique. Ces avantages ont établi les architectures verticales comme fondement de l’évolution ultérieure des wafers IGBT vers des configurations à arrêt de champ.

Intégration et optimisation de la technologie à tranchée

Procédés de formation de tranchées profondes

La mise en œuvre de structures en tranchée dans la fabrication de wafers IGBT représente une intégration sophistiquée de techniques avancées de traitement des semi-conducteurs avec un contrôle dimensionnel précis. La formation de tranchées profondes nécessite des procédés de gravure spécialisés, capables de créer des parois latérales verticales dont le rapport hauteur/largeur dépasse 10:1, tout en maintenant des dimensions de largeur uniformes sur l’ensemble de la surface du wafer. Ces procédés utilisent une chimie plasma soigneusement contrôlée ainsi que des configurations de champ magnétique afin d’atteindre la sélectivité de gravure et le contrôle de profil requis.

L'optimisation du procédé pour la production de wafers IGBT à tranchée implique des interactions complexes entre l'uniformité de la vitesse de gravure, la régularité des parois latérales et la précision dimensionnelle sur des densités de motifs variables. Des systèmes avancés de surveillance en continu du procédé suivent sans interruption l'évolution de la profondeur de gravure, les variations de l'angle des parois latérales et les niveaux de contamination de surface afin d'assurer des résultats constants. L'intégration de systèmes de commande avec rétroaction en temps réel permet un ajustement automatique des paramètres du procédé afin de compenser les dérives des équipements et les variations d'un wafer à l'autre.

Les mesures de contrôle qualité relatives à la formation des tranchées comprennent des protocoles métrologiques complets qui vérifient la précision dimensionnelle, l'intégrité des parois latérales et la propreté de surface à plusieurs stades du procédé. L'analyse par microscopie électronique à balayage fournit une caractérisation détaillée des profils des tranchées et de la morphologie des parois latérales, tandis que la microscopie à force atomique permet une évaluation quantitative des paramètres de rugosité de surface. Ces techniques analytiques garantissent que chacun Wafer IGBT répond aux spécifications rigoureuses des étapes de traitement ultérieures.

Progrès dans la formation de l'oxyde de grille et le dépôt de polysilicium

La formation de couches d'oxyde de grille de haute qualité au sein de structures en tranchée soulève des défis techniques particuliers, nécessitant des procédés spécialisés de dépôt et de recuit. Une croissance conforme de l'oxyde sur les parois latérales verticales exige un contrôle précis de la cinétique d'oxydation et de la gestion des contraintes afin d'éviter la formation de défauts pouvant nuire à la fiabilité du composant. Les procédés avancés d'oxydation thermique utilisent des compositions ambiantes soigneusement régulées ainsi que des profils thermiques précis pour obtenir une répartition uniforme de l'épaisseur de l'oxyde dans l'ensemble de géométries tridimensionnelles complexes.

La formation d'électrodes de grille en polysilicium à l'intérieur des tranchées nécessite des procédés sophistiqués de dépôt chimique en phase vapeur garantissant un remplissage complet sans formation de vide ni concentration de contraintes. Les paramètres du procédé de dépôt doivent être optimisés afin d'obtenir une couverture de palier adéquate tout en conservant une uniformité de film et des propriétés électriques acceptables. Les procédés de planéarisation ultérieurs éliminent l'excédent de matériau en polysilicium tout en préservant la géométrie précise de l'électrode de grille et la planéité de surface requises pour les étapes métallurgiques suivantes.

La qualité de l'interface entre l'oxyde de grille et les électrodes en polysilicium influence directement les caractéristiques électriques et la fiabilité à long terme des dispositifs IGBT sur wafers à tranchée. Des techniques avancées de caractérisation, notamment les mesures de capacité-tension et l'analyse par pompage de charge, permettent d'évaluer en détail la densité d'états d'interface et le comportement de piégeage des charges. Ces mesures orientent les efforts d'optimisation des procédés afin de minimiser les défauts d'interface susceptibles de dégrader les performances de commutation ou de réduire la durée de vie opérationnelle.

Mise en œuvre et ingénierie de la couche d'arrêt de champ

Conception du profil d'implantation ionique

La couche d'arrêt de champ représente une innovation critique dans les technologies modernes Wafer IGBT technologie permettant un contrôle précis de la répartition du champ électrique au sein de la structure du dispositif. La mise en œuvre de couches d'arrêt de champ nécessite des procédés sophistiqués d’implantation ionique, qui créent des profils de dopage contrôlés à des profondeurs spécifiques dans le substrat de silicium. Les paramètres d’énergie et de dose d’implantation doivent être soigneusement optimisés afin d’obtenir les effets souhaités de façonnage du champ tout en conservant la compatibilité avec les exigences des traitements thermiques.

L'optimisation de la conception des profils de la couche d'arrêt de champ implique une modélisation complexe de la répartition du champ électrique et de la dynamique des porteurs sous diverses conditions de fonctionnement. Des outils avancés de simulation de dispositifs permettent d'évaluer différentes formes et concentrations de profils de dopage afin d'identifier les configurations qui maximisent la capacité de tension de blocage tout en minimisant leur incidence sur les performances de commutation. L'intégration des couches d'arrêt de champ nécessite une prise en compte attentive des effets d'interaction avec d'autres régions du dispositif, notamment la couche de dérive et la structure de collecteur.

La maîtrise de la fabrication pour la mise en œuvre de la couche d'arrêt sur le champ exige une surveillance précise des paramètres d'implantation et des procédés subséquents d'activation thermique. L'uniformité du courant du faisceau d'ions, la stabilité de l'énergie et la précision de la dose influencent directement le profil de dopage obtenu ainsi que les caractéristiques de performance des dispositifs. Les systèmes avancés de contrôle des procédés surveillent en continu les conditions d'implantation et fournissent un retour d'information en temps réel afin de garantir des résultats cohérents sur plusieurs lots de tranches IGBT.

Activation thermique et affinement du profil

L'activation thermique des couches d'arrêt de champ implantées nécessite des procédés de recuit soigneusement contrôlés, permettant d'activer les atomes dopants tout en minimisant la diffusion indésirable et la génération de défauts. Les cycles de recuit à haute température doivent être optimisés afin d'obtenir une activation électrique complète des espèces implantées, tout en préservant la forme précise du profil de dopage requise pour des performances optimales du dispositif. Des techniques avancées de traitement thermique rapide permettent un contrôle précis de la température et du temps afin d'atteindre les niveaux d'activation souhaités.

Les défis liés à l'intégration du procédé pour le traitement thermique des couches d'arrêt de champ comprennent la gestion des limitations du budget thermique et l'évitement de la dégradation des structures de dispositif déjà formées. Les conditions de recuit doivent être compatibles avec les exigences d'intégrité de l'oxyde de grille, tout en fournissant suffisamment d'énergie thermique pour l'activation des dopants. Plusieurs séquences de recuit peuvent être mises en œuvre afin d'obtenir une activation optimale tout en maintenant la compatibilité globale du procédé.

La caractérisation de l’efficacité de la couche d’arrêt de champ implique des essais électriques complets et une analyse physique afin de vérifier la bonne formation du profil et l’activité électrique. La spectrométrie de masse à ions secondaires fournit des profils détaillés de concentration des dopants, comparables aux cibles de conception et aux prédictions issues des simulations. Les mesures électriques, notamment les essais de tension de claquage et l’analyse capacité-tension, confirment le bon fonctionnement de la couche d’arrêt de champ ainsi que l’amélioration de ses performances.

Améliorations des performances et fonctionnalités modernes

Améliorations de la vitesse de commutation

La technologie moderne de wafers IGBT à champ arrêté (field stop) de type tranchée offre des améliorations substantielles en matière de vitesse de commutation par rapport aux dispositifs des générations précédentes. La combinaison d’une architecture de canal vertical et de couches de champ arrêté optimisées réduit les pertes de commutation en minimisant les effets de stockage de charge et en améliorant l’efficacité d’extraction des porteurs lors des transitions de blocage. Ces améliorations permettent d’atteindre des fréquences de commutation plus élevées tout en maintenant des niveaux de dissipation de puissance acceptables dans des applications exigeantes.

Les caractéristiques de performance en commutation des dispositifs avancés à base de wafers IGBT reflètent une optimisation sophistiquée de plusieurs paramètres de conception, notamment la densité de canaux, l’épaisseur de l’oxyde de grille et la résistivité de la couche de dérive. Les dispositifs modernes atteignent des temps de mise en conduction mesurés en centaines de nanosecondes, tout en conservant un comportement contrôlé lors de la mise hors tension, ce qui minimise la génération d’interférences électromagnétiques. Les capacités accrues de vitesse de commutation élargissent les application plage pour la technologie de wafers IGBT dans les systèmes de conversion d'énergie à haute fréquence.

Les essais de performance dynamique des dispositifs modernes à base de wafers IGBT utilisent des techniques avancées de caractérisation permettant de capturer le comportement transitoire dans des conditions de fonctionnement réalistes. Les méthodes d’essai à double impulsion permettent une mesure précise des pertes de commutation et des limites de la zone de fonctionnement sûr, tout en simulant les conditions réelles du circuit. Ces efforts complets de caractérisation garantissent que les améliorations de performance se traduisent par un fonctionnement fiable dans des applications pratiques.

Gestion thermique et progrès en matière de fiabilité

L'évolution de la technologie des wafers IGBT a intégré des progrès significatifs en matière de gestion thermique, ce qui améliore la fiabilité des dispositifs et prolonge leur durée de vie opérationnelle. Une uniformité améliorée de la répartition du courant, obtenue grâce à des conceptions à arrêt de champ en tranchée, réduit les effets de chauffage localisé et les concentrations de contraintes thermiques pouvant compromettre l’intégrité du dispositif. La capacité accrue de gestion du courant permet un fonctionnement à plus forte densité de puissance tout en maintenant des températures de jonction acceptables.

Les améliorations de la fiabilité des dispositifs modernes à base de wafers IGBT résultent d’une optimisation systématique des interfaces matériaux, de la propreté des procédés et des caractéristiques de conception structurelle visant à minimiser les mécanismes de défaillance. Des techniques avancées de traitement des wafers réduisent les niveaux de contamination et améliorent la qualité cristalline dans toute la structure du dispositif. La mise en œuvre de chemins de courant redondants ainsi que des caractéristiques améliorées de dissipation thermique renforcent la robustesse face aux sollicitations cycliques thermiques et électriques.

La validation de la fiabilité à long terme pour les technologies avancées de wafers IGBT implique des programmes complets de tests accélérés évaluant les performances des composants dans des conditions de température, d’humidité et de contrainte électrique accrues. L’analyse statistique des modes de défaillance et des mécanismes de dégradation fournit des retours précieux pour poursuivre l’optimisation de la conception et les efforts d’amélioration des procédés. Ces mesures d’amélioration de la fiabilité garantissent que les gains de performance ne compromettent pas la longévité opérationnelle attendue dans les applications industrielles.

FAQ

Quelles sont les principales différences entre les structures de wafers IGBT planaires et en tranchée ?

Les structures de wafers IGBT à tranchée présentent des canaux de grille verticaux gravés dans la surface du silicium, tandis que les conceptions planes utilisent des canaux horizontaux formés au niveau de la surface. L’architecture verticale des structures à tranchée permet une densité de canal plus élevée par unité de surface, des pertes de conduction réduites et une capacité améliorée de gestion du courant. Les conceptions à tranchée offrent également un meilleur contrôle de la répartition du champ électrique et permettent des agencements d’appareils plus compacts par rapport aux configurations planes.

En quoi la couche d’arrêt de champ améliore-t-elle les performances du wafer IGBT ?

La couche d'arrêt de champ crée un profil contrôlé du champ électrique qui améliore la capacité de blocage de tension tout en réduisant les pertes lors des commutations. Cette région dopée, conçue sur mesure, empêche la concentration du champ électrique et permet d’utiliser des régions de dérive plus minces sans compromettre les valeurs nominales de tension de claquage. La mise en œuvre de l’arrêt de champ permet de réduire la chute de tension à l’état passant et d’accélérer les transitions de commutation, améliorant ainsi de façon significative le rendement global du dispositif dans les applications électroniques de puissance.

Quels défis de fabrication sont associés à la production de wafers IGBT à tranchée avec arrêt de champ ?

La fabrication de dispositifs à semiconducteurs IGBT à champ enterré nécessite un contrôle précis des procédés de gravure profonde, de la croissance conforme d’oxyde et des profils d’implantation ionique. La géométrie tridimensionnelle complexe exige des mesures avancées de surveillance des procédés et de contrôle qualité afin d’assurer des performances uniformes sur toute la surface de la plaquette. L’intégration de plusieurs étapes de traitement sophistiquées accroît la complexité de la fabrication et requiert une optimisation approfondie des procédés pour atteindre des niveaux de rendement acceptables.

En quoi l’évolution de la technologie des plaquettes IGBT a-t-elle influencé les applications en électronique de puissance ?

L'évolution vers la technologie de wafers IGBT à arrêt de champ en tranchée a permis des améliorations significatives de l'efficacité de conversion de puissance, des capacités de fréquence de commutation et de la fiabilité du système. Ces progrès ont élargi les possibilités d'applications dans les systèmes d'énergie renouvelable, les groupes motopropulseurs des véhicules électriques (EV) et les variateurs de moteur haute performance. Les caractéristiques de performance améliorées permettent des systèmes électroniques de puissance plus compacts, avec des besoins réduits en refroidissement et une efficacité globale du système accrue.

Table des matières

- Phases historiques du développement de l’architecture des wafers IGBT

- Intégration et optimisation de la technologie à tranchée

- Mise en œuvre et ingénierie de la couche d'arrêt de champ

- Améliorations des performances et fonctionnalités modernes

-

FAQ

- Quelles sont les principales différences entre les structures de wafers IGBT planaires et en tranchée ?

- En quoi la couche d’arrêt de champ améliore-t-elle les performances du wafer IGBT ?

- Quels défis de fabrication sont associés à la production de wafers IGBT à tranchée avec arrêt de champ ?

- En quoi l’évolution de la technologie des plaquettes IGBT a-t-elle influencé les applications en électronique de puissance ?