Máxima flexibilidad de diseño y posibilidades de integración

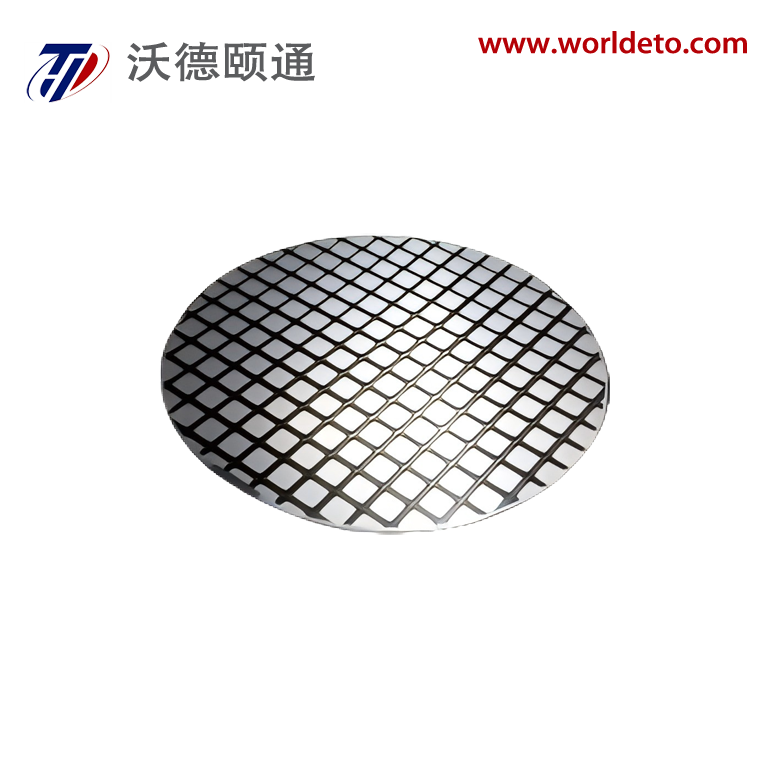

Los chips en estado bruto (bare die) desbloquean una flexibilidad de diseño sin precedentes que permite a los ingenieros crear soluciones innovadoras adaptadas a requisitos específicos de la aplicación. Esta flexibilidad proviene de la ausencia de restricciones predeterminadas de empaquetado, que normalmente limitan las opciones de conexión, las configuraciones de montaje y los enfoques de integración. Los ingenieros pueden implementar esquemas personalizados de unión por alambre (wire bonding), conexiones tipo flip-chip o técnicas avanzadas de empaquetado, como vías pasantes de silicio (through-silicon vias) y empaquetado a nivel de oblea (wafer-level packaging). La libertad de diseño se extiende también a la selección del sustrato, lo que posibilita el uso de materiales especializados, como circuitos flexibles, sustratos cerámicos o incluso estructuras tridimensionales de interconexión. Los diseños de módulos de múltiples chips (multi-chip module) se vuelven altamente prácticos con chips en estado bruto, permitiendo a los diseñadores integrar múltiples funciones provenientes de distintas tecnologías semiconductoras sobre un único sustrato. Esta capacidad de integración resulta invaluable para soluciones de sistema-en-un-paquete (system-on-package), donde es necesario que componentes analógicos, digitales y de radiofrecuencia coexistan en ensamblajes compactos. La flexibilidad abarca asimismo factores de forma personalizados, capaces de adaptarse a restricciones mecánicas únicas o a requisitos estéticos específicos. Los diseñadores pueden crear ensamblajes curvados, perfiles ultradelgados o formas irregulares que serían imposibles de lograr con componentes empaquetados estándar. Técnicas avanzadas de interconexión —como apilamiento de chips (chip stacking), interposers y capas de redistribución (redistribution layers)— se vuelven accesibles, posibilitando una integración de alta densidad y un mejor rendimiento eléctrico. La flexibilidad de diseño se extiende también a los procedimientos de prueba y validación, permitiendo interfaces de prueba personalizadas y métodos especializados de evaluación de fiabilidad. Los ingenieros pueden implementar esquemas de protección específicos para cada aplicación, configuraciones de blindaje electromagnético y enfoques de sellado ambiental adaptados a condiciones operativas particulares. Las posibilidades de integración incluyen diseños de sistemas heterogéneos que combinan distintos procesos semiconductores, tecnologías de memoria y bloques funcionales especializados. El enrutamiento personalizado de interconexiones permite optimizar las trayectorias de señal, reducir la interferencia electromagnética y mejorar las redes de distribución de potencia. Asimismo, esta flexibilidad favorece la prototipación rápida y los procesos iterativos de diseño, acelerando los ciclos de desarrollo de producto y permitiendo una entrada más ágil al mercado.